## (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 110491895 A (43)申请公布日 2019.11.22

(21)申请号 201910668693.4

(22)申请日 2019.07.23

(71)申请人 北京工业大学 地址 100124 北京市朝阳区平乐园100号

(72)发明人 郭伟玲 邰建鹏 申栗繁 孙捷

(74)专利代理机构 北京思海天达知识产权代理 有限公司 11203

代理人 沈波

(51) Int.CI.

H01L 27/15(2006.01)

H01L 33/00(2010.01)

H01L 33/38(2010.01)

H01L 33/48(2010.01)

权利要求书2页 说明书4页 附图4页

## (54)发明名称

NP电极共平面倒装Micro-LED微显示阵列及制作方法

#### (57)摘要

本发明公开了NP电极共平面倒装Micro-LED 微显示阵列及制作方法,包括电致发光阵列、倒装结合层、阵列倒装基板;电致发光阵列包括:像素单元、像素单元隔离槽、衬底;像素单元包括:N型半导体、有源区、P型半导体、绝缘层、N型电极、P型电极;阵列倒装基板包括:基板衬底、P电极互连线,N电极互连线、绝缘层。对外延材料进行干法刻蚀至N型半导体得到电极沟槽,并将像素单元隔离成两部分,然后生长绝缘层对电极沟槽侧壁进行保护,再溅射电极。使用干法刻蚀至衬底得到像素隔离槽,实现相邻像素电隔离。本发明采用倒装加共晶焊\回流焊方式可以提高芯片金属电极与下基板接触面积,从而提高热传导效率和机械强度。

1.NP电极共平面倒装Micro-LED微显示阵列,其特征在于:包括,电致发光阵列(1)、倒装结合层(17)、倒装基板(15);

其中电致发光阵列(1)包括多个发光二极管像素单元(13)、像素单元隔离槽(8)和衬底(2),像素单元隔离槽(8)设置在各个发光二极管像素单元(13)之间;每个所述的发光二极管像素单元(13)包含N型半导体(3)、N型电极(7)、有源区(4)、P型半导体(5)、P型电极(6)、电极沟槽(9)和绝缘层(12);通过MOCVD方法将N型半导体(3)制作在衬底(2)上面,量子阱有源区(4)制作在N型半导体(3)上面,P型半导体制作在量子阱有源区(4)上面;通过ICP干法刻蚀形成电极沟槽(9);通过PECVD制作绝缘层(12)包覆住电极沟槽(9),并腐蚀掉位于电极沟槽(9)底部的绝缘层(12),露出N型半导体(3);通过溅射/蒸镀方法制作N型电极(7)、P型电极(6);

倒装基板(15)从下至上分别是基板衬底(18)、在基板衬底(18)表面上的X电极互联线(11)、开有电极窗口(14)的绝缘层(12)、Y电极互联线(10);倒装结合层(17)设置在Y电极互联线(10)和X电极互联线(11)上。

2.根据权利要求1所述的NP电极共平面倒装Micro-LED微显示阵列,其特征在于:所述N型电极(7)包括三部分:

位于电极沟槽(9)底部与N型半导体接触的部分;

位于侧壁上的部分,所述部分仅覆盖外侧侧壁,并通过绝缘层(12)与侧壁隔离;

位于台面上的部分,并通过绝缘层(12)与台面隔离;位于台面上的部分用于和倒装基板Y电极互联线(10)焊接。

3.根据权利要求1所述的NP电极共平面倒装Micro-LED微显示阵列,其特征在于:所述绝缘层(12)包括两部分:

位于电极沟槽(9)外侧壁表面,用于隔离N型电极(7)与P型半导体(5)、有源区(4);

位于电极沟槽(9)内侧壁表面,用于保护N型半导体(3),有源区(4)。

4.根据权利要求1所述的NP电极共平面倒装Micro-LED微显示阵列,其特征在于:所述的X电极互联线(11)包括三部分:

位于四周的压焊焊盘(16)部分;

位于电极窗口(14)中央,用于倒装连接P型电极(6)的圆形焊盘部分:

连接焊盘16和圆形焊盘的部分。

5.根据权利要求1所述的NP电极共平面倒装Micro-LED微显示阵列,其特征在于:Y电极 互联线(10)包括三部分:

位于四周的压焊焊盘(16)部分;

位于电极窗口(14)四周,用于倒装连接N型电极(7)的圆环形焊盘部分,其中电极窗口(14)的直径大于圆形焊盘直径,小于圆环形焊盘内径;

连接压焊焊盘(16)和圆环形焊盘的部分。

- 6.根据权利要求1所述的NP电极共平面倒装Micro-LED微显示阵列,其特征在于:将制作好的电致发光阵列(1)整片或者沿隔离槽(8)切割后的发光二极管像素单元(13)通过倒装方式,转移至倒装基板(15)上。

- 7.根据权利要求1所述的NP电极共平面倒装Micro-LED微显示阵列,其特征在于:Y电极互联线(10)和X电极互联线(11)的交叉点为像素单元。

8.根据权利要求1所述的NP电极共平面倒装Micro-LED微显示阵列,其特征在于:P电极使用Cr/Pt/Au合金;

电致发光阵列(1)采用蓝宝石衬底(2)GaN外延材料,所述GaN外延材料至少包含依次形成在所述蓝宝石衬底上的N型半导体(3)、量子阱有源区(4)P型半导体(5);

绝缘层(12)使用SiO2、SiNx、聚酰亚胺绝缘导电层。

9.根据权利要求1所述的NP电极共平面倒装Micro-LED微显示阵列,其特征在于:基板 衬底(18)采用AlN、Cu或Al材料;

倒装结合层(17)选用导电胶、In、AuSn、AuSi或AuGe材料。

- 10.NP电极共平面倒装Micro-LED微显示阵列的制作方法,其特征在于:

- S1.清洗蓝宝石衬底GaN外延材料;

- S2. 在外延材料上使用光刻胶做为掩膜,保护不需要刻蚀的区域,通过ICP干法刻蚀电 致发光面板至N型半导体,形成电极沟槽(9);

- S3.通过PECVD,在外延材料上制备一层绝缘层(12),然后旋涂光刻胶,曝光显影将需要腐蚀掉的区域光刻胶去掉,再通过湿法腐蚀将不需要的绝缘层腐蚀掉,留下绝缘层(12);

- S4. 旋涂光刻胶,曝光显影将需要制备电极的区域光刻胶去掉,再通过溅射/蒸镀并剥离方法,制备N型电极(7),P型电极(6);快速热退火形成良好欧姆接触;

- S5.使用光刻胶或Si0<sub>2</sub>作为掩膜,ICP干法刻蚀外延材料至衬底,形成像素单元隔离槽(8);

- S6. 在基板衬底(18)上制备X电极互连线11方法同S4;

- S7.在X电极互联线(11)上制备绝缘层(12),并腐蚀出电极窗口(14),方法同S3;

- S8. 在绝缘层 (12) 上制备Y电极互联线 (10), 步骤同S4;

- S9. 电致发光阵列(1)通过倒装结合层(17)与倒装基板(15)进行结合。

## NP电极共平面倒装Micro-LED微显示阵列及制作方法

## 技术领域

[0001] 本发明涉及一种倒装微显示阵列芯片的结构和制作流程,属于Micro-LED微显示阵列技术领域,尤其涉及NP电极共平面倒装Micro-LED微显示阵列及制作方法。

## 背景技术

[0002] LED (Light emitting diode) 在显示领域有着不可替代的作用。相比于传统CTR、LCD甚至如今市场火爆的OLED显示技术,以Micro-LED微显示阵列技术为基础的微显示技术有着响应速度快,有源发光,对比度高,使用寿命长等优势。阵列结构分为主动和被动驱动,相比与主动结构,被动驱动以行列扫描方式来显示图像,外部驱动简单,但由于内部互联电极需要直接淀积在Micro-LED微显示阵列上,涉及跨越隔离槽,这使得互联电极可靠性差。若某点出现断路,则整行/列不能点亮,且不易定位。

[0003] 而且,Micro-LED微显示阵列散热是一个问题,在阵列中热量不易散出,积聚在芯片内部,从而降低芯片的性能和可靠性。

[0004] 本发明通过将被动驱动的Micro-LED微显示阵列内部互连线制备在倒装基板上,再通过倒装方式将阵列芯片和基板结合,从而解决互连线跨越深隔离槽带来的可靠性差问题。并且采用倒装与共晶焊\回流焊方式可以提高芯片金属电极与下基板接触面积,从而提高热传导效率和机械强度。

[0005] 因此需要一种的可靠性高的新型共平面倒装Micro-LED微显示来解决上述问题。

## 发明内容

[0006] 本发明的目的在于提供了一种NP电极共平面倒装Micro-LED微显示阵列以及对应的倒装基板的结构和制作方法,用以提高器件的可靠性。

[0007] 为实现上述目的,本发明采用的方案如下:

[0008] NP电极共平面倒装Micro-LED微显示阵列,包括:电致发光阵列1、倒装结合层17、倒装基板15。

[0009] 其中电致发光阵列1包括多个发光二极管像素单元13、像素单元隔离槽8和衬底2,像素单元隔离槽8设置在各个发光二极管像素单元13之间。每个所述的发光二极管像素单元13包含N型半导体3、N型电极7、有源区4、P型半导体5、P型电极6、电极沟槽9和绝缘层12。通过MOCVD方法将N型半导体3制作在衬底2上面,量子阱有源区4制作在N型半导体3上面,P型半导体制作在量子阱有源区4上面;通过ICP干法刻蚀形成电极沟槽9;通过PECVD制作绝缘层12包覆住电极沟槽9,并腐蚀掉位于电极沟槽9底部的绝缘层12,露出N型半导体3;通过溅射/蒸镀方法制作N型电极7、P型电极6。

[0010] 其中所述N型电极7包括三部分:

[0011] 位于电极沟槽9底部与N型半导体接触的部分:

[0012] 位于侧壁上的部分,所述部分仅覆盖外侧侧壁,并通过绝缘层12与侧壁隔离;

[0013] 位于台面上的部分,并通过绝缘层12与台面隔离;位于台面上的部分用于和倒装

基板N互联电极10焊接。

[0014] 所述绝缘层12包括两部分:

[0015] 位于电极沟槽9外侧壁表面,用于隔离N型电极7与P型半导体5、有源区4;

[0016] 位于电极沟槽9内侧壁表面,用于保护N型半导体3,有源区4。

[0017] 倒装基板15从下至上分别是基板衬底18、在基板衬底18表面上的P电极互联线11、 开有电极窗口14的绝缘层12、N电极互联线10。倒装结合层17设置在N电极互联线10和P电极 互联线11上:

[0018] 其中所述的P电极互联线11包括三部分:

[0019] 位于四周的压焊焊盘16部分;

[0020] 位于电极窗口14中央,用于倒装连接P型电极6的圆形焊盘部分;

[0021] 连接焊盘16和圆形焊盘的部分;

[0022] 所述的N电极互联线10包括三部分:

[0023] 位于四周的压焊焊盘16部分;

[0024] 位于电极窗口14四周,用于倒装连接N型电极7的圆环形焊盘部分,其中电极窗口14的直径大于圆形焊盘直径,小于圆环形焊盘内径;

[0025] 连接焊盘16和圆环形焊盘的部分;

[0026] 将制作好的电致发光阵列1整片或者沿隔离槽8切割后的发光二极管像素单元13通过倒装方式,转移至倒装基板15上;

[0027] N电极互联线10和P电极互联线11的交叉点为像素单元;

[0028] 优选地,P电极使用高反射率和欧姆接触更好的Cr/Pt/Au等合金,来降低P电极对光的吸收,提高出光效率:

[0029] 优选地,电致发光阵列1采用蓝宝石衬底2GaN外延材料;所述GaN外延材料至少包含依次形成在所述蓝宝石衬底上的N型半导体3、量子阱有源区4、P型半导体5;

[0030] 优选地,绝缘层12使用SiO<sub>2</sub>、SiNx、聚酰亚胺等绝缘导电层:

[0031] 优选地,基板衬底18采用导热性良好的材料,如AlN,Cu、Al等材料。

[0032] 优选地,倒装结合层17选用导电胶、In、AuSn、AuSi或AuGe等材料。

## 附图说明

[0033] 结合下图做进一步说明。

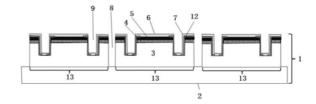

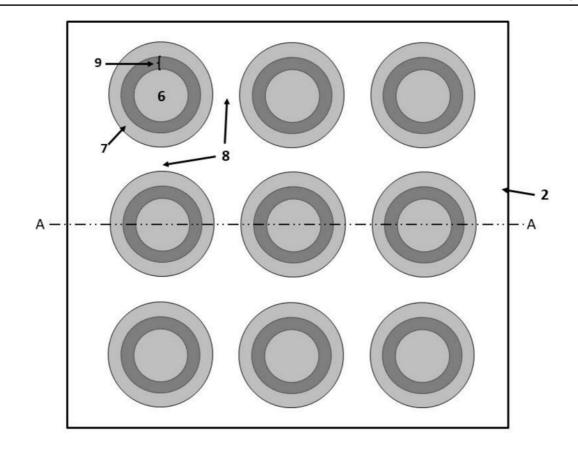

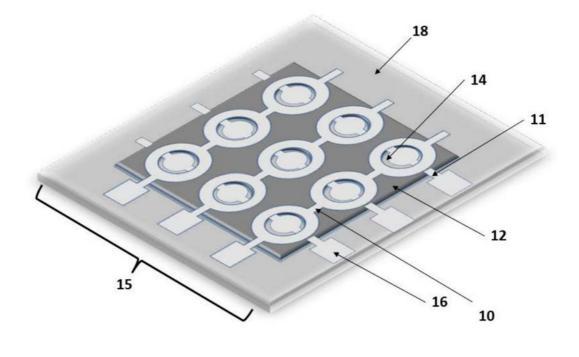

[0034] 图1是制作好的3×3NP电极共平面倒装Micro-LED微显示阵列芯片的俯视图;

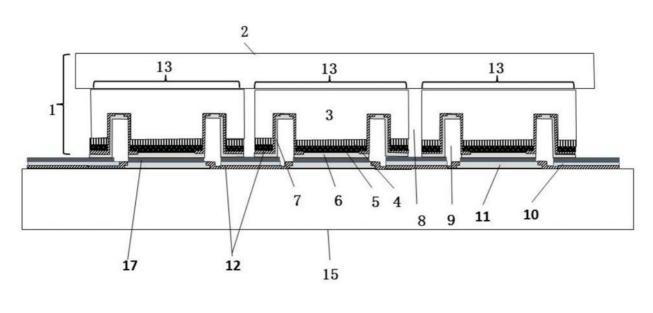

[0035] 图2是图1A-A截面图:

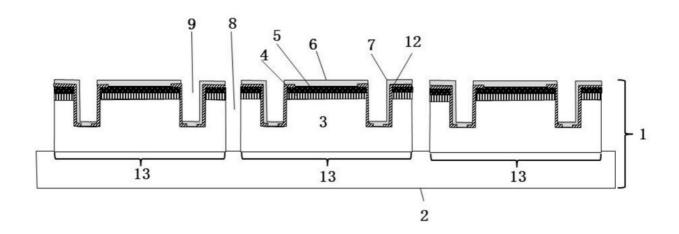

[0036] 图3是倒装基板的3D结构图:

[0037] 图4是3×3NP电极共平面倒装Micro-LED微显示阵列倒装到基板后的截面图:

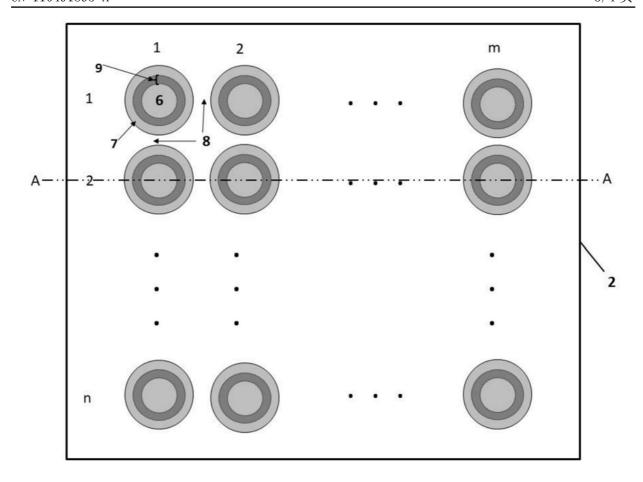

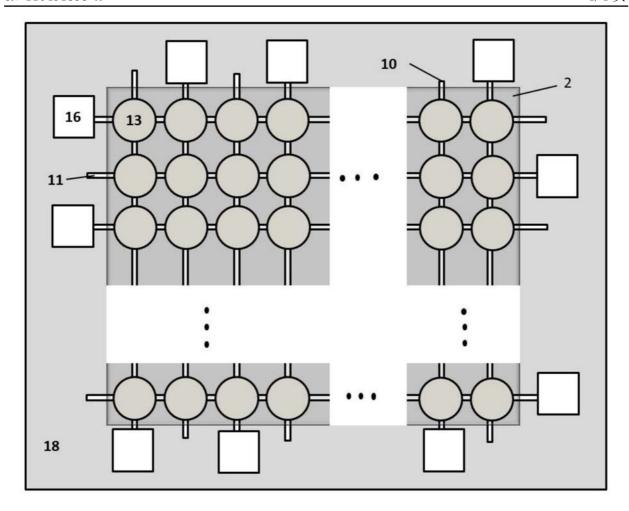

[0038] 图5是制作好的m×n共平面LED阵列芯片的俯视图;

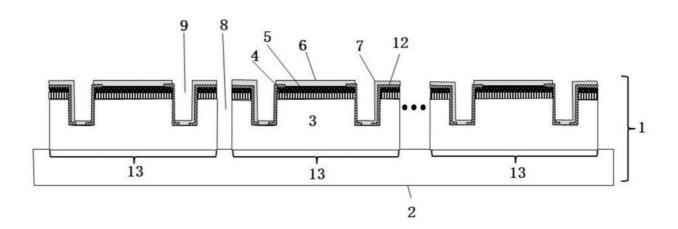

[0039] 图6是图5A-A截面图;

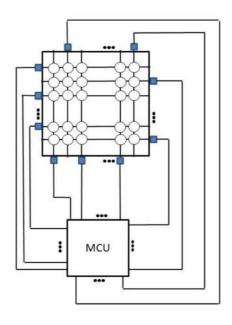

[0040] 图7是m×n的NP电极共平面倒装Micro-LED微显示阵列与倒装基板键合后的示意图:

[0041] 图8是外部驱动Micro-LED微显示阵列结构示意图;

[0042] 图中,1、电致发光阵列;2、衬底;3、N型半导体;4、有源区;5、P型半导体;6、P型电

极;7、N型电极;8、像素隔离槽;9、电极沟槽;10、N电极互连线;11、P电极互连线;12、绝缘层;13、发光二极管像素单元;14、电极窗口;15、倒装基板;。16、压焊焊盘;17、倒装结合层;18、基板衬底。

## 具体实施方式

[0043] 参考图1,图2一种NP电极共平面倒装Micro-LED微显示阵列,包括:

[0044] 衬底2:

[0045] N型半导体3,其制作在衬底2上面;

[0046] 有源区4,制作在N型半导体3上面;

[0047] P型半导体5,制作在有源区4上面;

[0048] NP电极沟槽9,通过刻蚀外延材料至N型半导体形成;

[0049] P电极6,制作在P型半导体上面;N电极7,制作在绝缘层12上面,并在电极沟槽9底部外侧壁延伸至台阶上面;

[0050] 像素隔离槽8,通过刻蚀外延材料至衬底形成,使LED像素单元电隔离;

[0051] 参考图3一种共平面倒装基板15,包括:

[0052] 基板衬底18:

[0053] P电极互连线11,制作在基板衬底18上面;

[0054] 开有电极窗口14的绝缘层12,制作在P电极互连线11上面,用于隔离P电极互联线和N电极互联线:

[0055] 焊盘16;用于键合金丝,连接外部驱动器;

[0056] 结合图1,本发明提供一种NP电极共平面倒装Micro-LED微显示阵列的制作方法,包含如下步骤:

[0057] 步骤1:在外延材料上刻蚀至N型半导体3内,形成NP电极沟槽9;

[0058] 步骤2:在完成步骤1的外延材料上制备一层绝缘层12,腐蚀位于电极沟槽9底部绝缘层12并露出N型半导体3;腐蚀掉P型半导体上面的绝缘层12并露出P型半导体5;

[0059] 步骤3:在绝缘层12和P型半导体5上部制备N电极7、P电极6,其中N电极7从电极沟槽9底部延电极沟槽9外侧壁延伸至台阶上,P电极在P型半导体上面:

[0060] 步骤4:刻蚀完成步骤3的外延材料至衬底2,形成像素单元隔离槽8;

[0061] 结合图3,一种倒装基板的制作方法,包含如下步骤:

[0062] 步骤5:在平整、干净的、绝缘的基板衬底18上通过溅射/蒸镀方法制备P电极互连线11:

[0063] 步骤6:在完成步骤5的P电极互联线11上面,通过PECVD方法制备绝缘层12:

[0064] 步骤7:通过湿法腐蚀方法腐蚀绝缘层12,形成电极窗口14;

[0065] 步骤8:在完成步骤7的绝缘层12上面制备N电极互连线10:

[0066] 下面结合图2,图3详细阐述NP电极共平面倒装Micro-LED微显示阵列及倒装基板的制作,方法如下:

[0067] S1.清洗蓝宝石衬底GaN外延材料:

[0068] S2.在外延材料上使用光刻胶做为掩膜,保护不需要刻蚀的区域,通过ICP干法刻蚀外延片至N型半导体,形成台阶隔离槽9;

[0069] S3.通过PECVD,在外延材料上制备一层绝缘层12,然后旋涂光刻胶,曝光显影将需要腐蚀掉的区域光刻胶去掉,再通过湿法腐蚀将不需要的绝缘层腐蚀掉,留下绝缘层12;

[0070] S4. 旋涂光刻胶,曝光显影将需要制备电极的区域光刻胶去掉,再通过溅射/蒸镀并剥离方法,制备N型电极7,P型电极6;快速热退火形成良好欧姆接触。

[0071] S5.使用光刻胶或SiO2作为掩膜,ICP干法刻蚀外延材料至衬底,形成隔离槽8;

[0072] S6.在基板衬底18上制备P电极互连线11方法同S4;

[0073] S7.在P电极互联线11上制备绝缘层12,并腐蚀出电极窗口14,方法同S3;

[0074] S8.在绝缘层12上制备N电极互联线10,步骤同S4;

[0075] S9.电致发光阵列1通过倒装结合层17与倒装基板15进行结合。

[0076] 以上所述,仅为本发明的具体实施方式,以上结构和实施例只用于帮助理解本发明方法和核心思想。对于本技术领域的普通技术人员来说,在不脱离本发明核心思想的前提下,还可以对本发明进行改进和修饰,这些改进和修饰也落入本发明权力要求的保护范围内。

图1

图2

图3

图4

图5

图6

图7

图8

| 专利名称(译)        | NP电极共平面倒装Micro-LED微显示阵列及制作方法                                         |         |            |  |

|----------------|----------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | CN110491895A                                                         | 公开(公告)日 | 2019-11-22 |  |

| 申请号            | CN201910668693.4                                                     | 申请日     | 2019-07-23 |  |

| [标]申请(专利权)人(译) | 北京工业大学                                                               |         |            |  |

| 申请(专利权)人(译)    | 北京工业大学                                                               |         |            |  |

| 当前申请(专利权)人(译)  | 北京工业大学                                                               |         |            |  |

| [标]发明人         | 郭伟玲<br>孙捷                                                            |         |            |  |

| 发明人            | 郭伟玲<br>邰建鹏<br>申栗繁<br>孙捷                                              |         |            |  |

| IPC分类号         | H01L27/15 H01L33/00 H01L33/38 H01L33/48                              |         |            |  |

| CPC分类号         | H01L27/156 H01L33/0066 H01L33/0075 H01L33/38 H01L33/48 H01L2933/0016 |         |            |  |

| 代理人(译)         | 沉波                                                                   |         |            |  |

| 外部链接           | Espacenet SIPO                                                       |         |            |  |

## 摘要(译)

本发明公开了NP电极共平面倒装Micro-LED微显示阵列及制作方法,包括电致发光阵列、倒装结合层、阵列倒装基板;电致发光阵列包括:像素单元、像素单元隔离槽、衬底;像素单元包括:N型半导体、有源区、P型半导体、绝缘层、N型电极、P型电极;阵列倒装基板包括:基板衬底、P电极互连线,N电极互连线、绝缘层。对外延材料进行干法刻蚀至N型半导体得到电极沟槽,并将像素单元隔离成两部分,然后生长绝缘层对电极沟槽侧壁进行保护,再溅射电极。使用干法刻蚀至衬底得到像素隔离槽,实现相邻像素电隔离。本发明采用倒装加共晶焊回流焊方式可以提高芯片金属电极与下基板接触面积,从而提高热传导效率和机械强度。